In most cases, application code can be written in C or other high-level languages. However, a basic understanding of the Cortex-M processor support instruction set can help developers choose the right Cortex-M processor for their specific application. The instruction set (ISA) is part of the processor architecture and the Cortex-M processor can be divided into several architectural specifications.

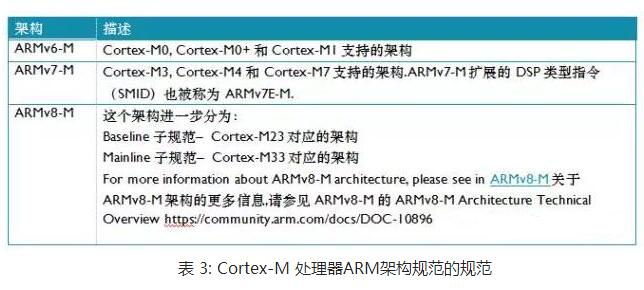

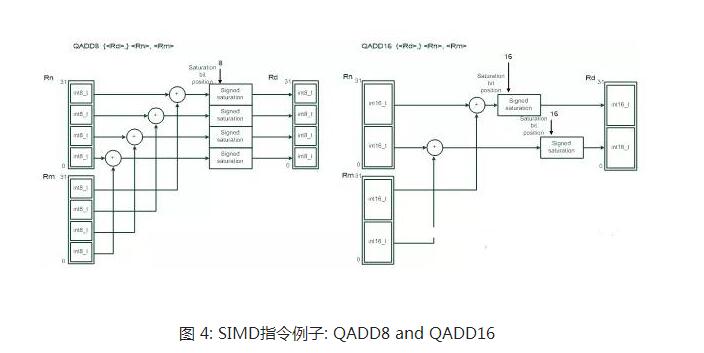

All Cortex-M processors support the Thumb instruction set. The entire Thumb instruction set became quite large when extended to the Thumb-2 version. However, different Cortex-M processors support different subsets of the Thumb instruction set, as shown in Figure 3.

The Cortex-M0/M0+/M1 processor is based on the ARMv6-M architecture. This is a small instruction set that only supports 56 instructions. Most of the instructions are 16-bit instructions. As shown in Figure 3, only a small part of the instruction set is used. However, the length of the registers and the processed data in this type of processor is 32 bits. For most simple I/O control tasks and ordinary data processing, these instructions are sufficient. Such a small instruction set can achieve processor design with a small number of circuit gates, Cortex-M0 and Cortex-M0+ minimum configuration is only 12K gates.

However, many of these instructions cannot use the high registers (R8 to R12) and have a limited ability to generate immediate data. This is the result of balancing ultra-low power consumption and performance requirements.

3, Cortex-M3 instruction setThe Cortex-M3 processor is an ARMv7-M based processor that supports a richer instruction set, including many 32-bit instructions that efficiently use high-order registers. In addition, M3 also supports:

Look up table jump instructions and conditional execution (using IT instructions)

Hardware division instructions

Multiply and add instruction (MAC)

Various bit manipulation instructions

A richer instruction set enhances performance in several ways; for example, 32-bit Thumb instructions support a wider range of literals, jump offsets, and address offsets for memory data ranges. Supports basic DSP operations (for example, supports several MAC instructions that require multiple clock cycles to execute, as well as saturating arithmetic instructions). Finally, these 32-bit instructions allow a single instruction to perform bucket shift operations on multiple data together.

Supporting richer instructions leads to greater area cost and higher power consumption. In a typical microcontroller, the Cortex-M3 has twice the number of circuit gates as Cortex-M0 and Cortex-M0+. However, the area of ​​the processor is only a small part of most modern microcontrollers, and the extra area and power consumption are often not so important.

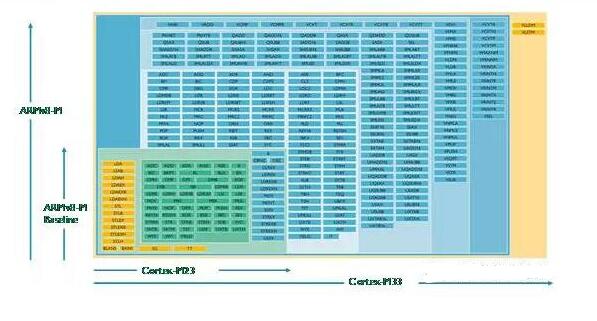

4, Cortex-M4 instruction setCortex-M4 is the same as Cortex-M3 in many places: pipeline, programming model. Cortex-M4 supports all the functions of Cortex-M3, and additionally supports various DSP-oriented applications such as SIMD, Saturated Operation Instructions, and a series of single-cycle MAC instructions (Cortex-M3 supports only a limited number of MAC instructions, and is multi-cycle Implemented), and optional single-precision floating-point operations.

The Cortex-M4 SIMD operation can process two 16-bit data and four 8-bit data in parallel. For example, the QADD8 and QADD16 operations shown in Figure 4:

In some DSP operations, using SIMD can speed up the faster calculation of 16-bit and 8-bit data because these operations can be processed in parallel. However, in general programming, the C compiler does not fully utilize SIMD computing capabilities. This is why the Cortex-M3 and Cortex-M4 benchmark scores are similar. However, unlike the Cortex-M4's internal data path and the Cortex-M3, the Cortex-M4 can handle faster (in some cases, a single-cycle MAC can be written back to two registers in one cycle).

5, Cortex-M7 instruction setThe instruction set supported by Cortex-M7 is similar to Cortex-M4 and adds:

Floating point data architecture is based on FPv5, not Cortex-M4 FPv4, so Cortex-M7 supports additional floating point instructions

Optional double-precision floating-point data processing instructions

Supports cached data prefetch instructions (PLDs)

The Cortex-M7 pipeline is very different from the Cortex-M4. The Cortex-M7 is a 6-stage dual emission pipeline that achieves higher performance. Most software designed for the Cortex-M4 can run directly on the Cortex-M7. However, in order to take full advantage of pipeline differences to achieve the best optimization, the software needs to be recompiled, and in many cases, the software needs some minor upgrades to take full advantage of new features like Cache.

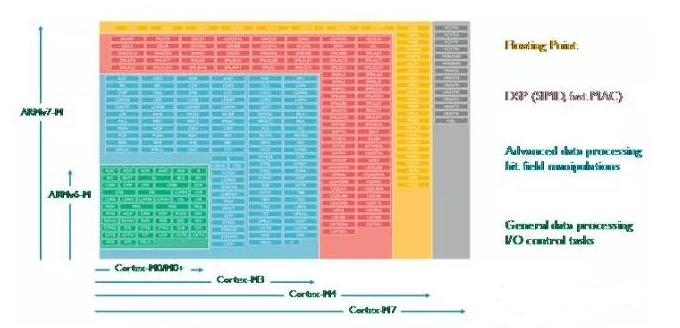

6, Cortex-M23 instruction setThe Cortex-M23 instruction set is based on the ARMv8-M Baseline sub-specification, which is a superset of ARMv6-M. Extended instructions include:

Hardware division instructions

Compare and jump instructions, 32-bit jump instructions

Supports TrustZone security extension instructions

Exclusive data access instructions (usually used for semaphore operations)

16-bit immediate number generation instructions

Load acquisition and store release instructions (supports C11)

In some cases, these enhanced instruction sets can improve processor performance and are useful for SoC designs that include multiple processors (for example, mutex access helps with multiprocessor semaphore processing)

7, I Cortex-M33 instruction setBecause the Cortex-M33 design is very configurable, some instructions are optional. E.g:

DSP instructions (supported by Cortex-M4 and Cortex-M7) are optional

Single-precision floating-point operations are optional. These instructions are based on FPv5 and are several more than the Cortex-M4.

Cortex-M33 also supports new instructions introduced by ARMv8-M Mainline:

Supports TrustZone security extension instructions

Load acquisition and store release instructions (supports C11)

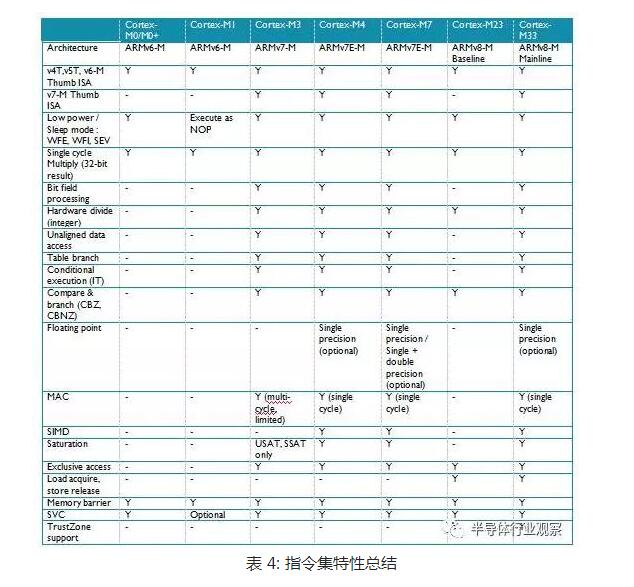

8. Comparison of instruction set featuresThe ARMv6-M, ARMv7-M, and ARMv8-M architectures have many instruction set features that make it difficult to cover all the details. However, the following table (Table 4) summarizes those key differences.

The most important feature of the Cortex-M processor instruction set is upward compatibility. Cortex-M3 instructions are a superset of Cortex-M0/M0+/M1. So, in theory, if the storage space allocation is consistent, the binary file running on the Cortex-M0/M0+/M1 can run directly on the Cortex-M3. The same principle applies to Cortex-M4/M7 and other Cortex-M processors; Cortex-M0/M0+/M1/M3 supported instructions can also run on Cortex-M4/M7.

Although the Cortex-M0/M0+/M1/M3/M23 processors do not have floating-point unit configuration options, the processor can still use software to do floating-point data operations. This also applies to products based on the Cortex-M4/M7/M33 but without floating point units. In this case, when a floating-point number is used in the program, the compiler toolkit inserts the required running software library during the linking phase. Software-based floating-point operations require longer runtimes and slightly increase code size. However, if floating-point arithmetic is not used frequently, this scheme is suitable for this application.

9 in 1 usb c adapter,10 In 1 Usb C Hub,usb-c multifunction adapter,type-c all-in-1 adapter macbook,USB C HUB,best USB-C Hubs

Shenzhen Konchang Electronic Technology Co.,Ltd , https://www.konchangs.com