Digital TV has developed very rapidly in the world, and the entire process of TV broadcasting, from the shooting, production, transmission to broadcast of programs, is gradually becoming digital. The emergence of MPEG video/audio compression standard solves the problem that the amount of information is too large and the channel bandwidth is limited after the digitization of TV signals; the continuous improvement of digital video hardware products has promoted the launch of various digital video products, bringing high to the audience. Quality picture and sound effects. All of this indicates that television broadcasting has entered the era of digitalization.

This article refers to the address: http://

Currently, the world's digital TV system standards include the European DVB system, the US ATSC system, and the Japanese ISDB system. These systems use the MPEG-2 standard for video compression [2], and China is actively developing its own digital TV standard. This article will introduce the chip SAA6752 produced by PHILIPS, which can implement MPEG-2 encoding in the development of products for the European DVB standard conventional digital TV and DVD front-end systems.

1 Main features of SAA6752

SAA6752, also known as EMPRESS, is PHILIPS' second-generation real-time MPEG-2 encoding chip. It integrates audio, video encoding and multiplexing into a single chip, and has a strong function. The external coding system can be realized by simply adding a related chip, thereby reducing system cost. At the same time, all video and audio compression algorithms run on EMPRESS's internal MIPS processor. The encoding software has been solidified in the chip. No additional software development is required. The system master chip can set the necessary encoding parameters through the I2C bus. . In addition, because it better solves the main problems in video coding - noise filtering and motion prediction, high-quality video encoding can be achieved at low bit rate, so that more video and audio can be stored on the storage medium. The purpose of the information.

The chip mainly provides the following functions [1]:

(1) Video compression

• Real-time MPEG-2 encoding (in accordance with MP@ML)

• Support resolution: D1, 2/3D1, 1/2D1 and SIF

• Support IPB, IP and I frame encoding in all modes

• Supported bit rate: 1.5 to 25 Mbps (for I frame encoding only)

1.5 to 15 Mbps (for IP frame encoding only)

1.5 to 15 Mbps (for IPB frame encoding only)

• Support CBR (Constant Bit Rate) and VBR (Variable Bit Rate)

• Has a programmable GOP (Group of Picture) structure

(2) Audio compression

• AC-3 audio encoding: 256kbps or 384kbps

• MPEG-1 Layer 2 audio coding (16 or 20 bits): 256kbps or 384kbps

(3) System reuse

• Reuse of video and audio streams in accordance with the MPEG system standard (ISO 13818-1)

• Generate and output MPEG-2 Transport Stream (TS), MPEG-2 Program Stream (PS), Packetized Elementary Stream (PES) and Elementary Stream (ES) in compliance with DVD, D-VHS and DVB standards

• Generate and insert MPEG time stamps (PTS/DTS/SCR/PCR)

2 MPEG-2 encoding system based on SAA6752

2.1 System Block Diagram

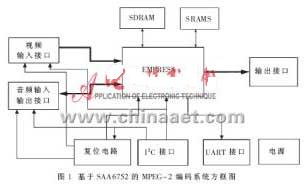

Because the SAA6752 does not have an on-chip CPU, in order to implement the encoding function, it must be controlled by an off-chip CPU. All control of the SAA6752 (such as rate control, PS stream and TS stream output, etc.) is done through the I2C bus [3], which is very simple. Figure 1 shows a block diagram of an MPEG-2 encoding system based on SAA6752.

The coding system is mainly divided into a video input part, an audio input/output part, an EMPRESS part, a reset part, an output interface, a power supply part, and an I2C and UART interface.

2.1.1 Video input section

The video input section provides two analog input interfaces, one for the CVBS signal and the other for the YC signal. This part can be done by PHILIPS SAA7114, all of which are controlled via the I2C bus.

2.1.2 Audio Input/Output Section

Since EMPRESS provides an audio I2S interface, this part mainly performs the function of converting analog audio into digital audio I2S signal.

2.1.3 EMPRESS section

Since the SAA6752 uses multiple processor modules, each processor and control module are independent of each other, so data transfer between modules is mainly realized by FIFO memory or external SDRAM. The system uses 16Mbit or 64Mbit SDRAM. The EMPRESS SAA6752 can generate a packed elementary stream whose code stream can be set according to different applications, one is a PES stream corresponding to the DVD format, and its code rate is variable; the other is the PES stream corresponding to the TS. , its code rate is constant.

2.1.4 Reset section

The system provides two reset modes: one is a hard reset; the other is a soft reset using I2C control software.

2.1.5 Output Interface Section

The system provides two TS parallel output interfaces: one is a TTL interface; the other is a standard LVDS interface.

2.2 Software Programming

In order to control the encoding of EMPRESS, an I2C interface line is used to connect the system to a computer for computer control of the EMPRESS chip, while initializing the SAA7114. All related operations are implemented through the I2C bus access registers. In the I2C control software, the I2C read and write addresses of EMPRESS and SAA7114 need to be determined.

EMPRESS I2C read and write address:

(1) When the I2C selection signal of EMPRESS is low, its I2C write address is 40H and the read address is 41H.

(2) When the I2C selection signal of EMPRESS is high, its I2C write address is 42H and the read address is 43H.

I2C read and write address of SAA7114:

(1) When the I2C selection signal of the SAA7114 is low, its I2C write address is 40H and the read address is 41H.

(2) When the I2C selection signal of the SAA7114 is high, its I2C write address is 42H and the read address is 43H.

In order to prevent the I2C address of EMPRESS and SAA7114 from conflicting, set the I2C selection signal of EMPRESS to low level, then the I2C write address of EMPRESS is defined as 40H; the I2C selection signal of SAA7114 is set to high level, then the I2C write of SAA7114 The address is defined as 42H.

The control software should implement the following I2C interface functions:

(1) Void I2C_Read_One_Byte(int address, int subaddress, int value)

This function mainly implements reading one byte of a given register, address determines the chip to be accessed, subaddress determines the register to be accessed, and value is the value of the return register.

(2) I2C_Write_One_Byte(int address, int subaddress, int value )

This function mainly implements writing a byte to a given register, address determines the chip to be accessed, subaddress determines the register to be accessed, and value is the value to be written to the register.

(3) I2C_Read_Muiti_Bytes(int address, int subaddress, int count, int *buffer)

This function mainly implements reading multiple bytes of a given register, address determines the chip to be accessed, subaddress determines the register to be accessed, and buffer returns multiple register values.

(4) I2C_Write_Multi_Bytes(int address, int subaddress, int count, int *buffer)

This function mainly implements writing to multiple bytes of a given register, address determines the chip to be accessed, subaddress determines the register to be accessed, and buffer is to write multiple register values.

By calling these functions, the on-chip registers of EMPRESS and SAA7114 can be set by the I2C interface.

With the I2C control software, the TS, PS, PES, and ES streams required for the generation and output of parameters (PID, code rate, etc.) can be arbitrarily modified. When the output code rate is set to 5 to 9 Mbit/s, a higher quality video image can be obtained.

The SAA6752 uses noise filtering and motion estimation techniques to enable the SAA6752-based MPEG-2 encoding system to provide high quality encoding for interfering input signals at low bit rate compression. This is especially suitable for applications that compress at lower bit rates, such as DVD video burning and Personal Video Recording.

While guaranteeing high coding quality, the SAA6752-based MPEG-2 coding system is designed to be very simple and easy to implement. When using this chip to design an MPEG-2 encoding system, it is only necessary to add a video analog/digital conversion chip, an audio analog/digital conversion chip and an external SDRAM to the periphery, and ordinary analog video and audio signals can be compressed into high quality MPEG. -2 video stream and MPEG-1 layer 2 or AC-3 audio stream, multiplexed into PS or TS, for storage or broadcast media. Since all video and audio coding algorithms and software are run on the on-chip processor, less system control resources are required. The main control chip only needs to set the encoding parameters through the I2C bus, without the user having more MPEG coding experience or investing too much design cost, shortening the design cycle.

Therefore, using the SAA6752 to design a low-cost, high-quality encoding system can be widely used in new consumer digital video products.

Fiber Optical Patch Panel,Fiber Optic Patch Panel,Fiber Optic Patch Panel Accessories,Fiber Optic Patch Cord Adapter

Huizhou Fibercan Industrial Co.Ltd , https://www.fibercan-network.com