To meet the market's need for more intensive processing and increased system integration, digital signal processing capabilities are already available for high-performance platform components. A new software-defined development process makes it easier for embedded software designers to use the C/C++ language.

Digital signal processing is the key technology required to implement basic equipment and services, including telecommunications networks, mobile communications, digital audio, streaming video, industrial motor control and machine vision, vehicle driving assistance, high performance radar, and Government information, etc.

To meet more complex system requirements, reduce latency, and increase channel capacity, dedicated digital signal processors (DSPs) have evolved into multi-core components with transmission rates up to tens of GFLOPS, either alone or in large multi-DSP combinations.

Despite this, the need for further development is still high, and equipment designers are working to increase system integration to reduce component count, enhance reliability, and reduce costs. In order to meet the requirements, the DSP extension version can now be integrated into a variety of platforms, from the ARM Cortex-M4 small embedded microcontroller (MCU) to FPGA and programmable system single chip (SoC). In addition, these high-performance configurable components are now ideally suited when designers face intensive processing that is only highly parallelizable, or if the system requires high-performance interfaces or custom accelerators.

The emerging DSP platform can be configured with SoCs to integrate a large number of DSP modules with system functions, including processors, memory, peripherals, and programmable logic components. For example, the Xilinx Zynq-7000 All Programmable SoC has up to 2,020 DSP slices, including a 25x8 multiplier, 48-bit accumulator, and related functions. In addition, the chip also has a dual-core ARM Cortex-A9 MPCore application processing unit, standard high-speed peripherals, including USB 2.0, Gigabit Ethernet, and volatile memory interfaces such as LPDDR2 and DDR3.

On the other hand, the multi-core processor Zynq MPSoC offers more resources, including up to 3,528 DSP partitions (each split contains a 27x18 amplifier) ​​plus PCIe Gen2, USB3.0, SATA 3.1 and DisplayPort peripherals. Support for DDR4 volatile memory. The MPSoC architecture also integrates the dual-core ARM Cortex-R5 MPCore real-time processing core, quad-core A53 and ARM Mali-400 MP2 graphics processing unit (GPU) and H.264/H.265 video codec.

The Zynq-7000 and MPSoC high-performance ARM processors also benefit from highly integrated NEON multimedia acceleration technology, FPGA DSP segmentation, integrated peripherals, and integration of up to 1143,000 logic cells in the UltraScale+ MPSoC. With these resources, the component can meet highly parallel processing and support a wide range of system integration needs, and beyond the traditional multi-core DSP level. For the design team, it is now a great moment to go beyond the performance limits of large multi-DSP development boards and let traditional DSPs jump to the All Programmable SoC platform. For example, using this technology, Xilinx engineers helped a customer redesign a radar motherboard that originally contained 32 traditional DSP chips, while the newly designed platform required only two programmable design components.

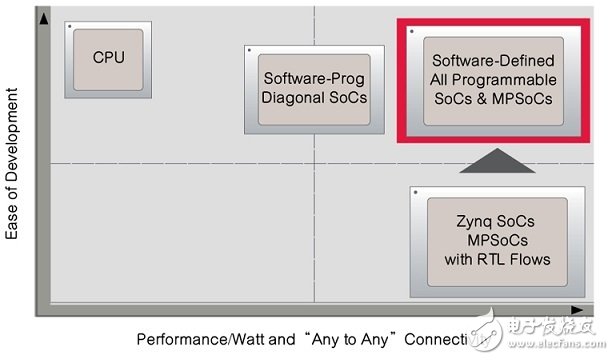

C/C++ Level Hardware Synthesis In the past, when designing programmable FPGAs and SoCs, engineers had to have hardware design skills to handle the stage-level (RTL) design, which made the design team that originally had software skills unable to fully utilize the additional features and Integration advantages. Figure 1 shows the trade-off between simplified software development and efficiency and flexibility. The figure compares traditional software programmable processors with programmable components at RTL or using software-defined design flows.

Figure 1: Software-defined process enables embedded software developers to fully understand the performance potential of All Programmable SoC components

Designing traditional DSP solutions has always been seen as a secure solution. However, as high-performance applications become more demanding, the design of high-performance DSPs is increasingly difficult to meet the requirements of multi-core architectures. Therefore, an ASSP-like programming experience is provided through the C/C++ design environment to assist systems and embedded software engineers in creating multiprocessing systems using the All Programmable SoC.

ASSP-like programming experience For example, Xilinx's SDSoC is an example of this development environment, and software engineers can develop C/C++ applications for programmable components without the need for traditional FPGA tools or hardware design languages ​​(HDL). In addition, it manages chip processing, DSP resources, and programmable hardware and memory to maximize system performance.

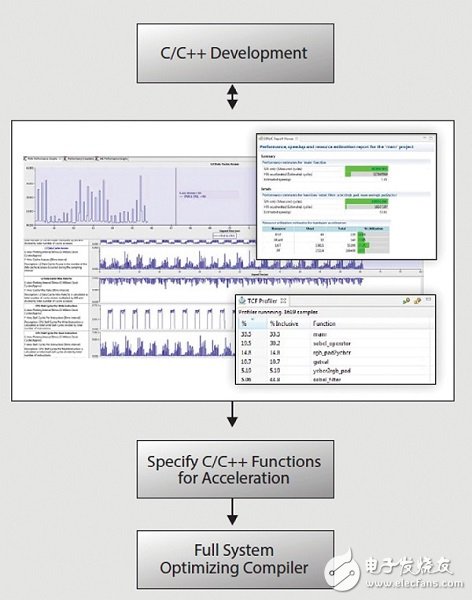

The environment includes a system-level characterization analyzer that understands the overall system performance and power consumption early in the design process. Figure 2 shows how the characterization analyzer works with the SDSoC process. The characterization analyzer quickly estimates system performance and indicates which C/C++ functions can be accelerated by programmable logic. The SDSoC then reports the software cycle through the code, estimates the data transfer time, and monitors hardware applications including cache, memory, and bus utilization.

This feature builds on the characterization capabilities of the Xilinx SDK and performs a complete design of hardware and software performance measurements on the Zynq platform. The quick estimation tool helps users quickly assess the performance impact of transferring one or more functions from software to hardware, and allows software developers to independently accelerate individual C/C++ functions in this way, thereby avoiding hardware and software teams. It takes a lot of interaction time and minimizes the number of iterations that the programmable logic needs to accelerate the software. Compared to hours or longer of hardware operation time, this method can evaluate the impact of the modification in just a few minutes.

Figure 2: Non-intrusive characterization analyzer based on PC samples

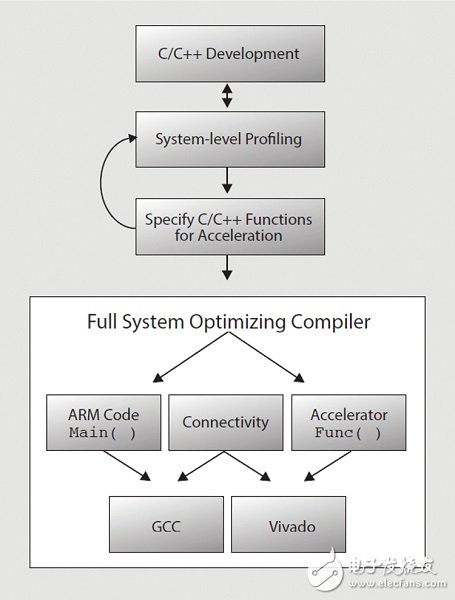

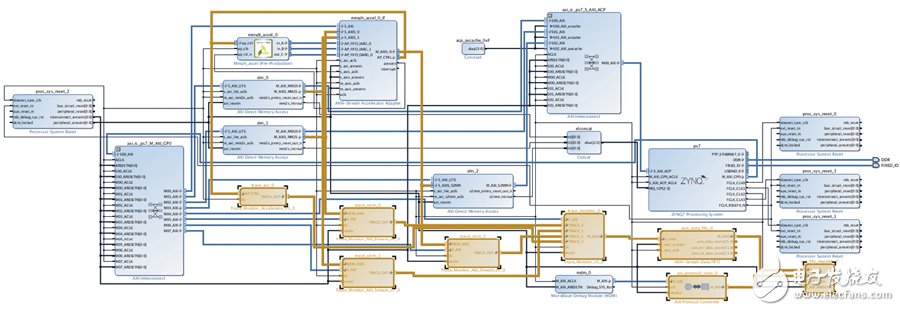

As shown in Figure 3, another C/C++ system-wide optimization compiler focuses on the SoC's ARM processor and programmable logic and connectivity. This compiler generates HDL code that is optimized for latency, bandwidth, and hardware utilization. The combination of a system-level feature analyzer and a system-optimized compiler can increase overall performance by a factor of 100 compared to software-centric solutions without hardware acceleration.

Figure 3: Full system compiler can control performance, transfer rate and latency to reduce design iteration time

System architects and platform developers with FPGA design technology can take advantage of SDSoC to create the best application platform for embedded software developers. The tool leverages automated system connectivity to generate features that help architects quickly understand the optimal interconnect structure between Zynq processing systems, memory and programmable logic accelerators.

In addition, architects can leverage the SDSoC of the Xilinx Vivado Design Suite to build platform-specific applications, configure traditional FPGA IP such as RTL descriptions, and serve as a library of available C libraries for reuse to increase design productivity.

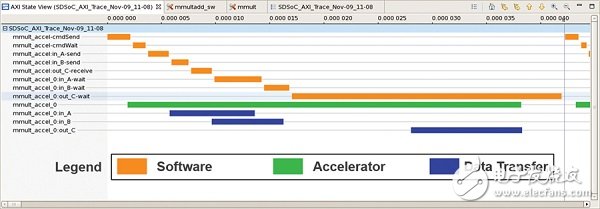

Software/hardware system performance analysis engineers can use SDSoC's trace tools to understand how their designs perform under different workloads, hardware and software partitions, and system designs. SDSoC Trace provides a detailed trace of the traces, including system events at the time of execution, software executed on the processor, hardware accelerator, and data transfer links within the system for tracking. The related events provide a timeline description in a graphical manner, and compared to the event record, the tracking can present interactive events within a certain period of time and help to further understand the application performance in the hardware and software system.

Figure 4a shows how SDSoC Trace automatically inserts a monitor into the hardware system; in addition, the trace meter is automatically inserted into the software system. Figure 4b shows the hardware and software trace stream to highlight different types of events.

Figure 4a: SDSoC Trace automatically inserts the necessary monitors and instrumentation functions after startup

Figure 4b: Trace visualization shows interactive events in hardware and software systems

The development board design supports the ZC702 and ZC706 based on the Zynq All Programmable SoC-based development board plus dedicated platforms provided by partners and specific markets, such as Zedboard, MicroZed, ZYB and AV and imaging development kits. SDSoC enables software engineering. And the development board design can work at the same time. In addition, each development board provides a support suite (BSP) that enables SDSoC to implement mediation data for abstract platforms, further enhancing productivity for embedded software developers and system architects, and accelerating product development timelines.

Conclusion Combining ARM/NEON application processing resources with a large number of DSP partitioning, FPGA architecture All Programmable SoC and MPSoC components, it is expected that DSP performance will exceed the current dedicated processor. The latest software-defined development environment has the advantage of allowing software engineers to independently leverage new components, while providing expert-level use cases for system architects and platform developers, making high-performance signal processing easier than ever.

Features

â—† Small Compact Size,Global safety approvals

â—† Long life & high reliability.

â—† Wide Range of wires Terminals.

â—†Variety of actuator and terminals

â—†Customized Designs

â—†Widely used in household appliances, electric force, telecommunications, machine tool, vessel, textile, printing, Mining machine, Mustic Instrument, etc.

Miniature Micro Switch,Ultra Miniature Micro Switch,Micro Miniature Slide Switch,Miniature Snap Action Switch

Ningbo Jialin Electronics Co.,Ltd , https://www.donghai-switch.com